# D4.2

# Demonstrator platforms accompanying report

| Due to stand how          |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Project number:           | ICT-644052                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Project acronym:          | HECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Project title:            | Hardware Enabled Crypto and Randomness                                                                                                                                                                                                                                                                                                                                                                                                            |

| Project Start Date:       | 1 <sup>st</sup> March, 2015                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Duration:                 | 36 months                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Programme:                | H2020-ICT-2014-1                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Deliverable Type:         | DEM                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Reference Number:         | ICT-644052 / D4.2/ 1.0                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Workpackage:              | WP4                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Due Date:                 | December 2017 - M34                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Actual Submission Date:   | $21^{st}$ December 2017                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Responsible Organisation: | TCS                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Editor:                   | Emeline Hufschmitt                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dissemination Level:      | PU                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Revision:                 | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Abstract:                 | Deliverable D4.2 contains the complete setup of the three<br>HECTOR demonstrators designed in the framework of work-<br>package WP4. The specifications of each demonstrator are<br>those described in D4.1. This document accompanying the<br>demonstrators gives a full description of each demonstrator<br>from motivation to user manual guide. Compliances to re-<br>quirements are completed and key performance indicators<br>highlighted. |

| Keywords:                 | Demonstrator, true random number generator, physically<br>unclonable function, authenticated encryption                                                                                                                                                                                                                                                                                                                                           |

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement no. 644052.

### Editor

Emeline Hufschmitt (TCS)

### Contributors (ordered according to beneficiary numbers)

Sandra Lattacher, Martin Deutschmann (TEC) Valdimir Rožić, Bohan Yang, David Singelée (KUL) Viktor Fischer, Oto Petura, Ugo Mureddu (UJM) Valentin Mascré (TCS) Bernard Kasser (STR) Ruggero Susella (STI) Marcel Kleja (MIC) Maria Eichlseder (TUG) Gerard van Battum, Marnix Wakker (BRT)

### Disclaimer

The information in this document is provided as is, and no guarantee or warranty is given that the information is fit for any particular purpose. The content of this document reflects only the author's view - the European Commission is not responsible for any use that may be made of the information it contains. The users use the information at their sole risk and liability.

# **Executive Summary**

Deliverable D4.2 consists of the complete setup of the demonstrator platforms. The aim of the demonstrators is to validate cryptographic primitives developed during the HECTOR project:

- True Random Number Generator,

- Physically Unclonable Function,

- Authenticated Encryption with Associated Data,

and to illustrate their relevance for the real-world security.

The three selected demonstrators, whose specifications are fully described in D4.1 [7], are the following:

**Demonstrator 1** Stand-alone, high performance secure random number generation device;

Demonstrator 2 Secure portable USB data storage;

**Demonstrator 3** Secure Messaging Device.

The demonstrators are implemented on two hardware platforms. While Demonstrator 2 and 3 are portable, small form-factor devices powered by the USB bus, Demonstrator 1 needing higher performance is powered by an external supply. The three demonstrators feature a USB interface to be connected to the host computer and a metallic case ensuring electric shielding and tamper evidence.

The demonstrators have been completely developed and validated and this document's purpose is to provide a summary of the motivations as well as high-level descriptions of the specifications, installation requirements and user guides for each demonstrator.

## HECTOR

# Contents

| 1 | Introduction                                                                                                                                                                                                                                | 1                                 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 2 | Demonstrator 1: Standalone, High Performance Secure Random NumberGeneration Device2.12.1Motivation2.2Description of the Demonstrator 1 Platform2.3Installation and User Manual2.4Conformance to Requirements and Key Performance Indicators | <b>2</b><br>2<br>2<br>9<br>14     |

| 3 | Demonstrator 2: Secure Portable USB Data Storage         3.1       Motivation                                                                                                                                                               | <b>16</b><br>16<br>16<br>23<br>31 |

| 4 | Demonstrator 3: Secure Messaging Device4.1Motivation4.2Description of the Demonstrator Platform4.3Installation and User Manual4.4Conformance to Requirements and Key Performance Indicators                                                 | <b>35</b><br>35<br>35<br>41<br>45 |

| 5 | Discussion on the Compliance with Recommendations R4 and R5 Given<br>by Reviewers During the Second Review Meeting in October 20165.1Recommendations R45.2Recommendation R5                                                                 | <b>48</b><br>48<br>50             |

| 6 | Summary and Conclusion                                                                                                                                                                                                                      | 52                                |

| 7 | List of Abbreviations                                                                                                                                                                                                                       | 53                                |

# List of Figures

| Functional block diagram of the HECTOR Demonstrator 1 platform          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block diagram of the HECTOR Demonstrator 1 hardware                     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HECTOR Demonstrator 1 hardware                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Block diagram of the PLL-TRNG core implemented in Altera Cyclone V FPGA |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| as a part of HECTOR Demonstrator 1                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Block diagram of the DC-TRNG design                                     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Block diagram of hardware in the Demonstrator 1 control device          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Block diagram of hardware means in Demonstrator 1 SoC                   | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Demonstrator 1 GUI welcome splash screen                                | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Demonstrator 1 GUI main screen                                          | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Demonstrator 1 GUI screen showing data acquisition details              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PC_DEMO2                                                                | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Demonstrator hardware platform                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FPGA top architecture.                                                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| demo2_main.pdf                                                          | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

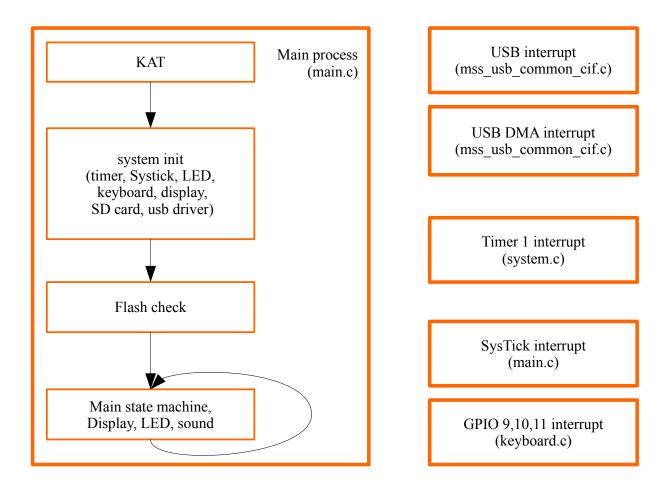

| Firmware modules.                                                       | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

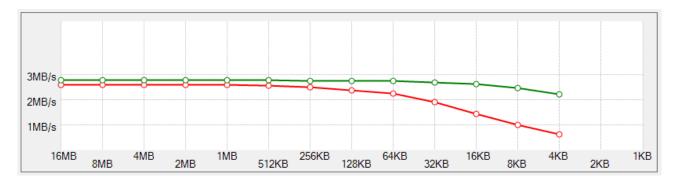

| Data transfer rate. Reading in green, writing in red                    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

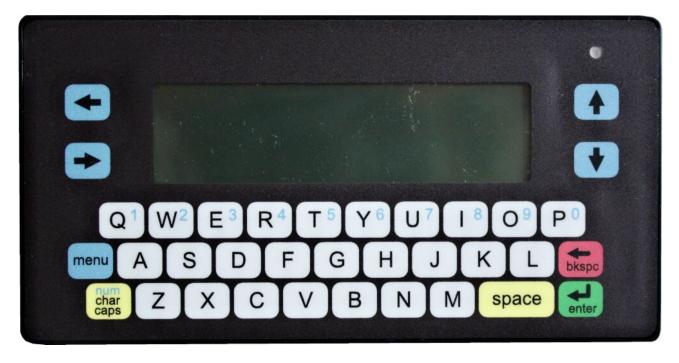

| The front panel of the device                                           | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

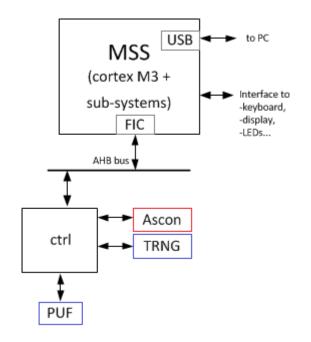

| HECTOR Demonstrator 3 overview                                          | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                         | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

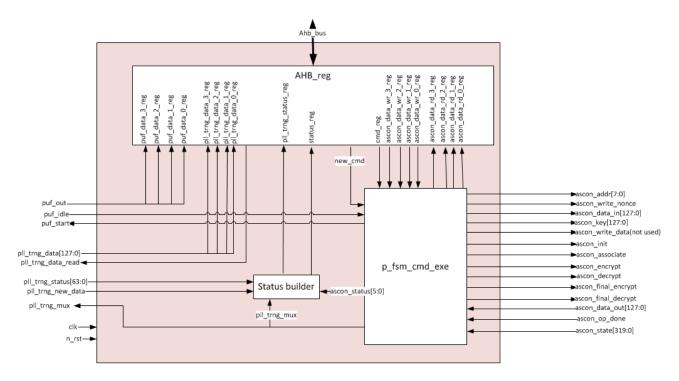

| Interface of the control block                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

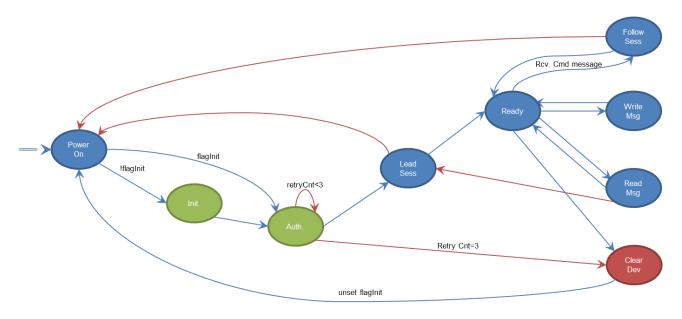

| Main state machine                                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ,                                                                       | Block diagram of the HECTOR Demonstrator 1 hardware         HECTOR Demonstrator 1 hardware         Block diagram of the PLL-TRNG core implemented in Altera Cyclone V FPGA         as a part of HECTOR Demonstrator 1         Block diagram of the DC-TRNG design         Block diagram of hardware in the Demonstrator 1 control device         Block diagram of hardware means in Demonstrator 1 control device         Block diagram of hardware means in Demonstrator 1 SoC         Demonstrator 1 GUI welcome splash screen         Demonstrator 1 GUI screen showing data acquisition details         PC_DEMO2         Demonstrator hardware platform         FPGA top architecture.         demo2_main.pdf         Firmware modules.         Data transfer rate. Reading in green, writing in red.         The front panel of the device .         HECTOR Demonstrator 3 overview         Demonstrator 3 hardware platform |

# Chapter 1

# Introduction

Deliverable D4.2 consists of the complete setup of the demonstrator platforms as output of T4.2 and T4.3. The software and hardware specifications of the HECTOR demonstrator platforms were fully detailed in D4.1. This deliverable includes the following items:

- the integration of the hardware modules in the platforms and system level design including control unit and communication interface,

- the development of a software interface accessing the hardware module from the PC via USB,

- the development of a user friendly GUI to observe the auditing capabilities.

Demonstrator 1 is a high throughput secure TRNG. It exploits two physical random number generators: a PLL-TRNG and a DC-TRNG. A typical application could be a personalization center where high volumes of high quality random numbers are required to initialize secure devices.

Demonstrator 2 is a secure portable USB data storage. It is a personal, single-user device used to protect data at rest. It implements a TERO-PUF, the AEAD algorithm ASCON 128-a, a PLL-based true random generator and a two-factor authentication protocol.

Demonstrator 3 is a secure messaging device which offers the possibility to exchange secure messages between two devices, over an insecure network and through untrusted PCs. It makes use of the same hardware platform as Demonstrator 2 but implements communications between host and PC differently in order to encrypt and authenticate stream of messages from one device to another.

This document is accompanying the platforms delivery. It is divided in three main chapters, each dedicated to one demonstrator. For each of them the motivation is first given, in order to give perspective to the demonstrator. Then each demonstrator specifications and building blocks are briefly described. Next part concerns installation and user manual description. Finally conformance to requirements are reviewed and completed.

The last chapter concerns recommendations R4 and R5 from the report of the second review meeting. Detailed answers are given using inputs from each demonstrator purpose and specification.

# Chapter 2

# Demonstrator 1: Standalone, High Performance Secure Random Number Generation Device

# 2.1 Motivation

The aim of Demonstrator 1 is to show that the proposed TRNG designs and especially the new stringent TRNG design approach can be successfully applied in high-end real-world data security applications, in which a secure and robust TRNG is an essential construction block. The proposed demonstrator could be used as a stand-alone security peripheral – the source of high quality random numbers – in high-performance data servers and communication systems. Demonstrator 1 could serve in the future as a high-speed random number generator, exploiting two physical random number generators: a PLL-TRNG and a DC TRNG. This kind of generators could find their typical application in personalization centers where high volumes of high quality random numbers are required to initialize a large quantity of devices.

The security evaluation of Demonstrator 1 shows its compliance with the AIS20/31 requirements [6], verification of the quality of the TRNG output, observation of entropy margins during variation of the TRNG operational conditions and verification if the behavior of the TRNG is in line with the stochastic model.

Besides being compliant with the AIS 20/31 document, HECTOR Demonstrator 1 is also compliant with the newly developed US standard NIST SP 800-90B [13] and stringent recommendations of the French DGA (Direction Générale de l'Armement), currently being edited. Simpler AIS 20/31 compliance demonstration lowers security evaluation and certification costs, which should result in having more products going through the certification process and increase confidence in the solution.

# 2.2 Description of the Demonstrator 1 Platform

Demonstrator 1 is a physical true random generator including cryptographic post-processing algorithm, which is aimed at generation of random bitstreams achieving security level PTG.3, as defined in AIS 20/31. The generation of random numbers is provided as a security service for the user.

### 2.2.1 Hardware Design

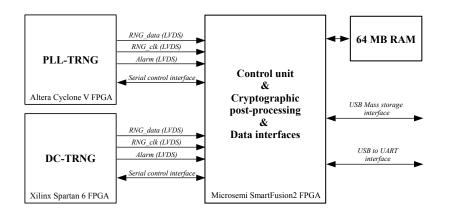

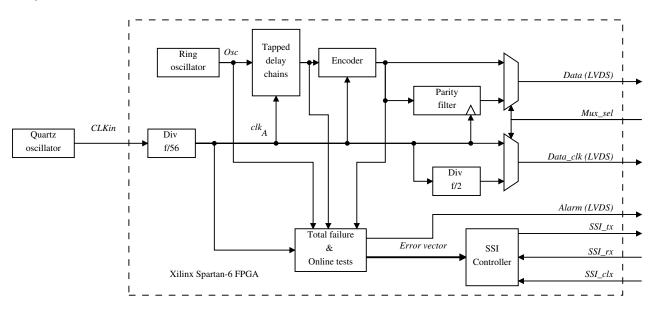

The functional block diagram of the Demonstrator 1 platform is depicted in Fig. 2.1. The main intellectual property (IP) blocks are implemented in three FPGAs:

- the Altera Cyclone V FPGA contains the phase-locked loop based TRNG (PLL-TRNG),

- the Xilinx Spartan 6 FPGA contains the delay chain based TRNG (DC-TRNG),

- the Microsemi SmartFusion2 FPGA contains a control unit based on the ARM Cortex M3 core, cryptographic post-processing block, and data interfaces including RAM memory interface.

The TRNG cores are connected to the main control FPGA using fast low voltage differential signaling (LVDS) interface used for data acquisition and slow synchronous serial interface used as control interface.

Raw random bit streams coming from the two TRNG cores are acquired (cryptographically post-processed or not) in the 64 MB RAM memory using the direct memory access (DMA). The memory is divided in two halves: one is used for data acquisition and the second one is used as a solid disk, which is accessible from the host computer (PC) as a data storage medium (mass storage device). Consequently, the maximum size of the acquired data block is 32 MB. Thanks to the DMA transfer and the use of fast data interface, no data is lost during data acquisition.

Figure 2.1: Functional block diagram of the HECTOR Demonstrator 1 platform

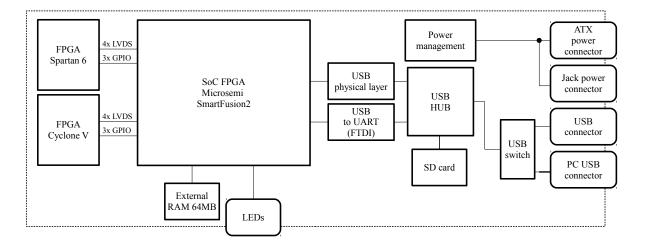

The block diagram of the Demonstrator 1 hardware is depicted in Fig. 2.2. Besides the three FPGA devices and the external memory presented in the previous paragraph, it contains a USB hub, and two USB interfaces (USB to UART convertor from the FTDI company and USB physical layer), an SD card connector, and other data and power connectors.

The SD card can contain device drivers, which can be downloaded to the host PC. Demonstrator 1 communicates with the host PC via two USB ports: a UART serial interface (virtual COM port) and a mass storage device interface. The UART port is used to send 64-bit commands or small data blocks and to receive 64-bit demonstrator state word or small data blocks. The mass storage device port is used to transfer high volume data files (up to 32 MB) from Demonstrator 1 to the host PC.

The Demonstrator 1 hardware is depicted in Fig. 2.3. Three FPGA areas visible in the picture are separated by a ground plate. They are closed in three separated chambers inside the metallic shielding.

Figure 2.2: Block diagram of the HECTOR Demonstrator 1 hardware

Figure 2.3: HECTOR Demonstrator 1 hardware

## 2.2.2 Description of the PLL-TRNG Core

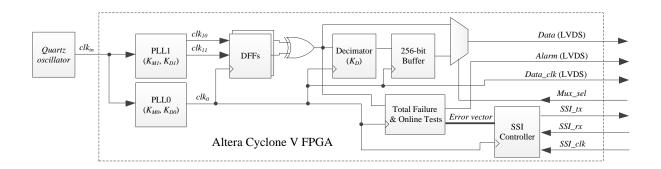

The final version of the PLL-TRNG proposed in the framework of the HECTOR project uses the differential jitter between two PLLs as a source of randomness. It is depicted in Fig. 2.4. The generator is accessible in two modes: Evaluator mode and User mode.

### Evaluator Mode

In Evaluator mode of the PLL-TRNG, two kinds of RNG core outputs can be obtained to verify its correct operation, including operation of the two PLLs, of the sampling flip-flop, and of the XOR gate:

1. **Output of the XOR gate** can be used to characterize the jitter and to verify correct operation of the two PLLs,

Figure 2.4: Block diagram of the PLL-TRNG core implemented in Altera Cyclone V FPGA as a part of HECTOR Demonstrator 1

2. Raw binary signal. Access to this signal is needed to apply Procedure B of the TRNG evaluation, in which tests T6 to T8 of AIS 31 need to be applied on the generated raw binary signal.

Availability of Evaluator mode is a very interesting option since it makes security evaluation of the generator much easier, especially by reducing the cost of certification.

The type of core output is selected using the  $Mux\_sel$  signal. By default, the raw random data output is selected.

### User Mode

In User mode of Demonstrator 1, the raw random bitstream featuring entropy rate per bit of at least 0.997 as required by AIS 20/31 is sent to the cryptographic post-processing block implemented in the SmartFusion2 device. In User mode, the user has thus access only to the cryptographically post-processed output signal.

### Parametric Statistical Tests

Output of the XOR gate is used internally by both the Total failure and Online tests. The Total failure test (test T0 [6]) counts number of random samples appearing in each of 255 periods  $T_Q$  (one period  $T_Q$  is composed of  $K_D$  periods of  $clk_0$ ). If no random sample was found, the Total failure alarm ( $Err_t 0$ ) is triggered and the system interrupt is requested. Two Online tests observing the XOR gate output are implemented:

Two Online tests observing the XOR gate output are implemented:

- the Online test T1 [6] computes parameter  $P_1$  corresponding to the number of random samples during subsequent periods  $T_Q$  (a period  $T_Q$  is the period of pattern appearing at the output of the XOR gate, which depends on frequency ratio of the clock signals generated in PLLs),

- the test T2 [6] computes parameter  $P_2$  corresponding to the variance of the clock jitter measured during 4080 periods  $T_Q$ .

Computed values  $P_1$  and  $P_2$  are compared with thresholds obtained from the stochastic model and required for the Shannon entropy rate per bit of 0.997 (4 <  $P_1$  <  $K_D/4$ , 228 <  $P_2$  < 1280). The execution time of the Online test (4080 periods  $T_Q$ , i.e. about 4 ms) represents a compromise between precision of entropy estimation and reactivity of the test. While guaranteeing a sufficient precision, it is much shorter than that of the fastest general-purpose statistical tests FIPS-140-1 [10], which need at least 20 000 random bits (i.e. almost 5 times more bits).

### 2.2.3 Description of the DC-TRNG Core

The Delay-Chain based TRNG uses jitter accumulated in a free-running ring oscillator as a source of randomness. It is depicted in Figure 2.5. The role of the tapped delay chain is to enable samplings from the output of the ring oscillator using very high timing resolution (approximately 17 ps on a Xilinx Spartan-6 FPGA). The data sampled by the delay chain is a digital representation of the waveform of the ring-oscillator output signal. Due to the white-noise sources that are present in all electronic circuits, the frequency of the free-running ring oscillator is not stable. Timing positions of the Ring Oscillator (RO) output signal edges, relative to the reference clock become more uncertain over time. The variance of this timing uncertainty is proportional to the jitter accumulation time (the period of the sampling signal  $clk_A$ ).

Figure 2.5: Block diagram of the DC-TRNG design

The output Osc of the entropy source (free-running ring oscillator) is connected to a delay line consisting of m = 40 serially connected delay buffers. The output of each buffer connects to a flip flop. These m flip-flops comprise an m-bit register that is clocked by the  $clk_A$  signal. This signal is obtained by down-sampling the reference clock signal provided by an on-board quartz oscillator. The down-sampling factor is a design parameter that is chosen to allow for a sufficient jitter accumulation time. The output of the register is connected to a priority encoder which encodes the position difference of two consecutive samples into a single output bit. The generator can work in two modes: Evaluator mode and User mode.

### **Evaluator Mode**

In Evaluator mode of the DC-TRNG, the raw random bits (before the algorithmic postprocessing) can be collected to derive parameters for online tests. This data output can be used as input for Procedure B of the TRNG evaluation, too. Tests T6 to T8 of AIS 31 can thus be applied on the raw random bits [6].

In order to provide an additional security margin while fulfilling the bitrate requirements of the output, a two-stage parity filter is used to improve the robustness of the TRNG core against possible active attacks. This two-stage parity filter XORs two consecutive raw random bits to generate one random bit. The output of the parity filter can be read in the DC-TRNG Evaluator mode, too.

### User Mode

In User mode of Demonstrator 1, the random bit output of the algorithmic post-processing is connected to the input of the cryptographic post-processing implemented in the SmartFusion2 device. The random bit sequence meets the AIS 20/31 requirements, according to which this input needs to feature a 0.997 entropy per bit as the lower bound.

### Embedded Statistical Tests

Two total failure tests are provided in this implementation. The first total failure test uses an edge detector to check whether the free-running ring oscillator is toggling or not. The edge detector is reset every two clock cycles. It triggers an alarm if the input signal has not changed. The second total failure test is designed to generate an alarm if there is no edge sampled in the tapped delay chain.

DC-TRNG contains two statistical tests that detect long-term weaknesses in the generated raw data bitstream. These two tests have different false-alarm rates. On-line test 1 (Sensitive test) has a higher false-alarm rate but is more efficient in detecting attacks. On line test 2 (Robust test) is less efficient in detecting attacks but it is more robust against false alarms. Both tests work on a sequence of 512 consecutive raw bits. The Online test 1 is counting the overlapping template 111 in the sequence. At the end of 512-bit sequence, the counter value is compared with the pre-computed upper and lower boundaries ( $35 < N_{111} < 93$ ). If the counter exceeds these boundaries, an alarm signal is generated. The false alarm rate of this test is 1%. Online test 2 is tracking the XORed result  $C_1$  of two consecutive bits in the 512 consecutive raw bits. At the end of the sequence, result value is computed and compared with the pre-computed boundaries ( $185 < C_1 < 326$ ). The false alarm rate of this test is  $10^{-6}$ .

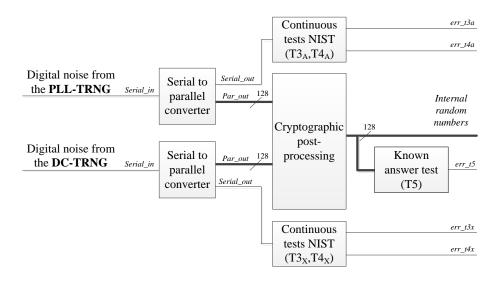

## 2.2.4 Description of the Control Device Hardware

The SmartFusion2 System on Chip (SoC) FPGA combines the FPGA fabric with a simple hardwired microcontroller sub-system (MSS). The role of the MSS and its firmware is explained in the next section. Besides the control logic accessible by the local microcontroller, which is described in the next section, the FPGA fabric in the Demonstrator 1 control device contains two serial-to-parallel converters, two sets of continuous tests and a cryptographic post-processing block (see Fig. 2.6). Two continuous tests ensure compliance with requirements of the French DGA and with those of NIST SP 800-90B [13]: the Repetition count test and Adaptive proportion test. Both tests evaluate continuously the raw random bit stream just before the cryptographic post-processing block (as required by NIST SP 800-90B). Consequently, they test correct operation of all RNG blocks until the cryptographic post-processing (and namely the decimator and serial-to-parallel converter in PLL-TRNG and the parity filter in DC-TRNG, which are not tested by dedicated tests of the two TRNGs, as required by the French DGA).

Figure 2.6: Block diagram of hardware in the Demonstrator 1 control device

The execution time of the Continuous tests is similar to that of Online tests (4096 periods  $T_Q$ , i.e. about 4 ms).

Results of functional and statistical tests are saved in a 64-bit state register. The contents of the state register is sent to the control interface of the RNG, which can be reached by the system processor of Demonstrator 1.

If any of the error bits is asserted, the RNG triggers a high speed alarm and a system interrupt is requested. At the same time, generation of the raw signal is stopped, input shift register of the cryptographic post-processing unit is not filled in any more, and consequently, the cryptographic post-processor will not get ready until the RNG is not reset by the system processor.

After the reset was asserted (not represented in Fig. 2.4), the startup procedure is launched and once succeeded, the random data can be available again.

## 2.2.5 MSS Firmware

The main role of the SmartFusion2 SoC FPGA in Demonstrator 1 is to communicate with the host PC, to create and to manage the file system, and to control data acquisition.

The acquired data are saved into one half of the RAM memory (data buffer), which accessible from the MSS. The MSS controls communication with the host PC via serial communication protocol (a COM bus) and creates, manages and exploits a file system, which is placed in the second half of the RAM memory and which is accessible from the PC as a USB mass storage device (see Fig. 2.7).

The heart of the MSS is a simple microcontroller hardwired in the SmartFusion2 device. It is based on the ARM Cortex M3 core. The Demonstrator 1 firmware is divided into few parts: a UART packetizer-depacketizer, a communication control unit and a USB mass-storage class driver.

The FPGA fabric in Demonstrator 1 contains RAM interface, a set of 32-bit data registers available for MSS, a command execution controller, and other associated logic.

Data acquisition is initialized by the host PC. The PC sends a command packet to the MSS a COM port. The command is decoded and sent into the communication control unit. The

Figure 2.7: Block diagram of hardware means in Demonstrator 1 SoC

control unit initializes the FPGA fabric, which starts to acquire selected data stream to the 64-MB RAM memory available inside the demonstrator. At the end of data acquisition, the MSS confirms execution of the command using a command confirmation packet, which is sent back to the PC. During data acquisition, the PC requests continuously MSS about evolution of the data acquisition process. After data acquisition, the host PC sends another command, which creates a file system in the demonstrator memory and copies the acquired data into a new binary file created in the file system. Demonstrator 1 is thus seen from the PC as a mass storage device and the newly created file can be read by the host PC using a mass storage device driver (i.e. Demonstrator 1 behaves as a USB key connected to the PC).

# 2.3 Installation and User Manual

In this section, we describe shortly hardware and software tools that constitute the Demonstrator 1 toolkit. Next, we describe steps needed to install Demonstrator 1 hardware and software. Finally, we present user interface and the way the demonstrator can be operated.

### 2.3.1 Prerequisites

The Demonstrator 1 toolkit is composed of the following hardware and software tools:

- Demonstrator 1 hardware including USB cable

- Demonstrator 1 power adapter

- Host PC including Windows 7, 8, or 10 or Linux operating system

- TCL interpreter. Windows TCL interpreter is embedded in the Demonstrator 1 software bundle. On Linux, following software must be installed:

- TCL version >= 8.5

- Tk version >= 8.5

- TkLib with Plotchart module

- Set of Demonstrator 1 control TCL scripts

- FTDI virtual com-port (VCP) driver

### 2.3.2 Installation

### Hardware Setup

Demonstrator 1 can be used as an external device or it can be installed inside a host desktop PC into the 3.5 inch rack. If it is used as an external device, the Demonstrator 1 power adapter must be used and plugged into the corresponding connector of the demonstrator. Then, the delivered USB cable (type A-B) must be used to connect demonstrator with the host PC. If Demonstrator 1 is used as an internal device, it must be first fixed in the 3.5-inch bay. Standard 10-wire flat USB cable and ATX power cable must be used to install the demonstrator hardware in the PC.

### Software Setup

Once the demonstrator hardware is installed and the demonstrator is powered and plugged into the external or internal USB bus, the availability of the FTDI VCP driver must be checked. In the Linux OS, the driver is installed by default, but Windows needs the driver to be installed manually. If the driver is installed, the operating system will assign a COM port to it. At this stage, the user has to determine manually, what is the COM port number that has been assigned to demonstrator. In Windows OS, this can be done using the Device manager. In Linux, the COM port is represented by a device node /dev/ttyUSBX, where X corresponds to the COM port number. This COM port number must be specified by the user in the graphical demonstrator interface as explained in the following section.

### 2.3.3 User Manual

Demonstrator 1 is accessible using the Tool Command Language (TCL) scripts, which describe the Graphical User Interface (GUI) and controls Demonstrator 1 functions. Before the demonstrator is used for random data acquisition or evaluation, its default parameters must be set up.

### Setting Up Default Parameters of Demonstrator 1

After the Demonstrator 1 is connected to the PC and its COM port is determined, one can launch the Demonstrator 1 GUI interface in order to communicate with the hardware. This can be done in Windows by running the run.bat file, or in Linux by running the tclsh gui.tcl command.

When launched, the Demonstrator 1 interface will greet the user with a welcome splash screen shown in Fig.  $2.8\,$

Figure 2.8: Demonstrator 1 GUI welcome splash screen

After the splash screen is closed, the main interface is presented (see Fig. 2.9). In this interface the user must specify initial parameters of Demonstrator 1:

- **HECTOR board COM port** full name of the COM port as determined in the previous section (COMX in Windows or /dev/ttyUSBX in Linux).

- File name (without extension) requested output file name. The software will automatically add a .bin suffix to this name. The acquired TRNG output data will be stored in the resulting file.

- File size [bytes] requested file size in bytes. This number must be a multiple of 4.

### Reset Demonstrator 1 and its Blocks

Once all the fields are set to correct values, the user can send commands to the Demonstrator 1 hardware. It is a good practice to reset Demonstrator 1 before it is used for the first time after the power up. This can be done through the Reset menu, which contains several items:

- Reset All resets all the connected hardware (SoC and both TRNGs).

- **Reset SoC** resets only the Microsemi SmartFusion2 SoC.

- Reset PLL TRNG resets only the PLL TRNG.

- **Reset DC-TRNG** resets only the DC-TRNG.

| HECTOR DEMO-1                 |           |                           |             |             |

|-------------------------------|-----------|---------------------------|-------------|-------------|

| Reset Get HW status Help      |           |                           |             |             |

| HECTOR board COM port         | COM4      |                           |             |             |

| File name (Without extension) | acq       | File size [bytes]         | 1250000     | Start       |

| Generator state               |           |                           |             |             |

| HW versions                   |           | SoC status                |             |             |

| Interface version             |           | PLL TRNG repetitions cou  | nt          |             |

| PLL TRNG core version         |           | PLL TRNG adaptive propo   | rtion count |             |

| DC-TRNG core version          |           | DC-TRNG repetitions cour  | nt          |             |

|                               |           | DC-TRNG adaptive propo    | rtion       |             |

| PLL TRNG                      |           | DC-TRNG                   |             |             |

| Parameter P1                  |           | Online test 1 feature cou | nt          |             |

| Parameter P2                  |           | Online test 2 feature cou | nt          |             |

| Max. repetitions              |           |                           |             |             |

| RO frequency                  |           |                           |             |             |

| Bitrate [kb/s]                |           |                           |             |             |

| 1100 -<br>1000 -<br>900 -     |           |                           |             |             |

| 800 -<br>700 -                |           |                           |             |             |

| 600-                          |           |                           |             |             |

| 500 -                         |           |                           |             |             |

| 400 -                         |           |                           |             |             |

| 300-160 kb/s                  |           |                           | 96 kb/s     |             |

| 200 - V                       | 28 kb/s   | 4 kb/s                    |             |             |

|                               |           |                           |             |             |

| TPM Infineon                  | TPM Intel | TPM Sinosun               | TPM Atmel H | HECTOR TRNG |

|                               |           |                           |             |             |

| 1                             |           |                           |             |             |

Figure 2.9: Demonstrator 1 GUI main screen

### **TRNG Status Request and Data Acquisition**

When the device is reset, the user can retrieve either only the status of the demonstrator, or its status as well as TRNG output data. Each time, a corresponding log file containing status of the demonstrator is created and saved in data directory. In order to retrieve status only, one can click on the *Get HW status* in the main menu.

In order to retrieve random data and TRNG status, the user must click on the *Start* button on the main screen. Data acquisition will then start and after it's finished, the Demonstrator 1 status together with output bit rate is reported on the main screen as shown in Fig. 2.10.

Parameters measured by online tests are shown along with their limiting values on the main screen under *Generator state*. If any of measured parameters is out of range, an error message is shown and data acquisition is terminated (no data is acquired).

If no error occurred, the binary file is created at a location specified by the user.

| HECTOR DEMO-1                                   |                                                               |

|-------------------------------------------------|---------------------------------------------------------------|

| Reset Get HW status Help                        |                                                               |

| HECTOR board COM port COM4                      |                                                               |

| File name (Without extension)                   | File size [bytes] 1250000 Start                               |

| File name (Without extension) acq               | File size [bytes]  1250000 Start                              |

|                                                 |                                                               |

| Generator state                                 |                                                               |

| HW versions                                     | -SoC status                                                   |

| Interface version 11                            | PLL TRNG repetitions count 25 (max. allowed 51)               |

| PLL TRNG core version 3.1                       | PLL TRNG adaptive proportion count 1133 (max. allowed 1380)   |

| DC-TRNG core version 5.7                        | DC-TRNG repetitions count 25 (max. allowed 51)                |

|                                                 | DC-TRNG adaptive proportion 1130 (max. allowed 1380)          |

| PLL TRNG                                        | -DC-TRNG                                                      |

| Parameter P1 15 (allowed interval: 4 - 46)      | Online test 1 feature count 46 (allowed interval: 35 - 93)    |

| Parameter P2 439 (alowed interval: 228 - 1280)  | Online test 2 feature count 257 (allowed interval: 185 - 326) |

| Max. repetitions 12                             |                                                               |

| RO frequency 271.4 MHz                          |                                                               |

|                                                 |                                                               |

| Bitrate [kb/s]                                  |                                                               |

| 1200                                            | 1042 kb/s                                                     |

| 1000 -                                          |                                                               |

| 900 -                                           |                                                               |

| 800 -                                           |                                                               |

| 700 -                                           |                                                               |

| 600 -<br>500 -                                  |                                                               |

| 400                                             |                                                               |

| 300 - 160 kb/s                                  |                                                               |

| 200 28 kb/s                                     | 96 kb/s                                                       |

| 100-                                            |                                                               |

| 0 TPM Infineon TPM Intel                        | TPM Sinosun TPM Atmel HECTOR TRNG                             |

|                                                 |                                                               |

| TRNG output bitrate: 1042.2094841063054 kbits/s |                                                               |

| ,                                               |                                                               |

Figure 2.10: Demonstrator 1 GUI screen showing data acquisition details

# 2.4 Conformance to Requirements and Key Performance Indicators

The following table shows the status of Demonstrator 1 regarding requirements defined in D1.2.

| Requirement                                                    | Current status                                         | Remark    |

|----------------------------------------------------------------|--------------------------------------------------------|-----------|

| Fu                                                             | nctional requirements                                  |           |

| Ready after 3 seconds                                          | < 4 ms                                                 | Satisfied |

| Output data rate over 1Mb/s                                    | 1.04 Mb/s                                              | Satisfied |

| Secure DRNG                                                    | DRG.3 Implemented                                      | Satisfied |

| Ha                                                             | ardware requirements                                   |           |

| Availability of an embedded pro-<br>cessor in the control FPGA | ARM Cortex M3 embedded<br>in SmartFusion2 FPGA         | Satisfied |

| USB connectivity between the control FPGA and the host PC      | USB Mass Storage Device<br>and UART interface used     | Satisfied |

| The use of up to 15k logic cells<br>in the control FPGA        | 5k logic cells                                         | Satisfied |

| The use of up to 10k logic cells<br>in FPGAs with RNG cores    | 1k (in Cyclone V) and 1k (in<br>Spartan 6) logic cells | Satisfied |

| Total USB consumption smaller<br>than 5W                       | 4.5 W                                                  | Satisfied |

| Data interface faster than 2<br>Mb/s                           | 16 Mb/s                                                | Satisfied |

| S                                                              | ecurity requirements                                   |           |

| TRNG is AIS20/31 PTG.3 com-<br>pliant                          | Validated by BrightSight                               | Satisfied |

| TRNG require less than 300mW                                   | 80 mW                                                  | Satisfied |

| TRNG startup tests require less<br>than 3 seconds to complete  | < 4 ms                                                 | Satisfied |

## 2.4.1 Key Performance Indicators

Table 2.4.1 shows main key performance indicators for Demonstrator 1.

| Key Performance Indicators for Demonstrator 1 |                                                                                                                                                                                                          |  |  |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Security                                      | <ul> <li>High security</li> <li>AIS20/31 [6] PTG.3 compliant</li> <li>NIST SP800-90B [13] compliant (online tests implemented)</li> <li>French DGA requirements (not published yet) compliant</li> </ul> |  |  |  |

| Speed                                         | Bitrate over 1 Mb/s – considerably higher than solutions benchmarked in [11]                                                                                                                             |  |  |  |

# Chapter 3

# Demonstrator 2: Secure Portable USB Data Storage

# 3.1 Motivation

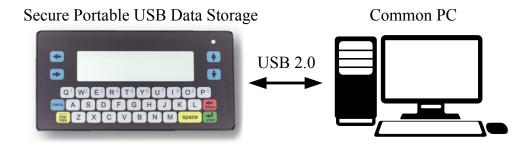

USB flash drive or USB memory are popular means of data storage, back-up and transfer. Such devices may contain sensitive personal information and/or company assets in digital form, e.g. bank statements, legal documents, commercial treaties, sales and billing documents, source codes, technical documentation or other intellectual property. The risk for the information to be compromised is high when commuting, travelling, or just leaving the drive unattended in a car or a hotel room. To **enhance privacy** one has to use a secure solution. Such a product then contains not only a flash memory and a USB interface but also a hardware encryptor. Vendors offer secure USB portable devices where data are protected by approved cryptographic algorithms, e.g. AES. However weaknesses have been discovered in existing solutions [4]. There is also a lack of trusted secure storage solutions engineered and manufactured in EU.

The goal of Demonstrator 2 is to show that the proposed cryptographic primitives, algorithms and protocols in HECTOR can be successfully applied in this real-world data security application, and that user and device authentications are sufficiently strong and secure.

Demonstrator 2 was also inspired by MICRONIC's **hardware platform** already available at the beginning of the project.

# 3.2 Description of the Platform

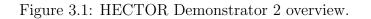

Demonstrator 2 is a secure portable USB storage, see Fig. 3.1. It is a personal, single-user

device. It protects the data stored on it while being at rest. It requires the user to authenticate before allowing access to data. It is powered from the USB bus without the need of an external power source.

The secure USB storage device contains encrypted data that can be unlocked by supplying a user passphrase code through the built-in demonstrator keyboard. In principle USB storage devices are physically controlled by the user of the device. Security is provided by the protection of the device itself and by the fact that the owner is the only person that knows the passphrase. The device has been designed to resist attacks in the "Lost and found" scenario. The data shall be secured at rest also when an attacker gains access to the not-activated device without knowing the passphrase. When found (or stolen), an attacker can only try a user defined number of passphrases before the device will permanently lock its data.

### 3.2.1 Hardware Design

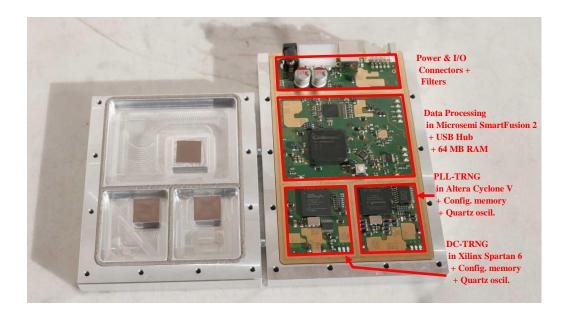

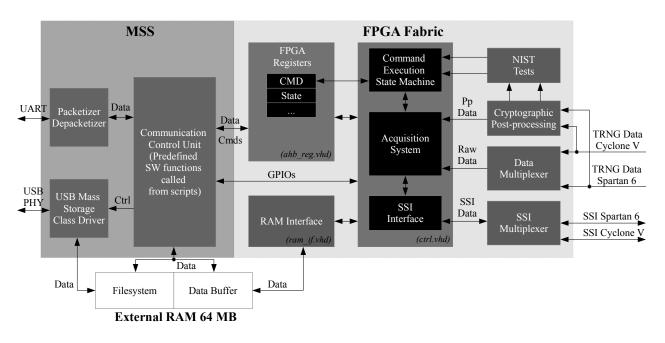

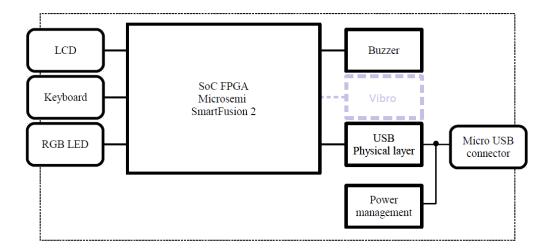

The hardware platform of demonstrator 2 is given in Fig. 3.2.

Figure 3.2: Demonstrator hardware platform.

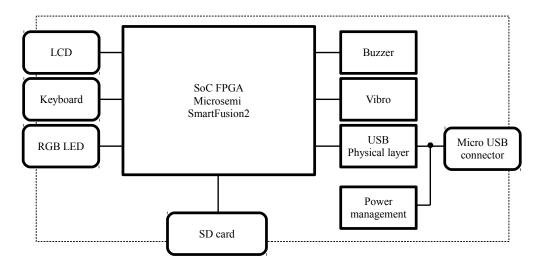

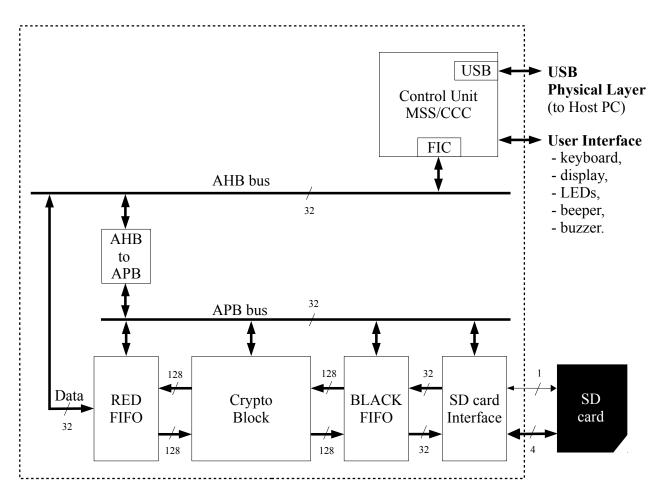

The HECTOR demonstrator integrates a SmartFusion2 SoC FPGA which consists of two parts:

- the Microcontroller Subsystem which integrates a Cortex M3 processor and other subsystems like SPI, I2C, USB controllers,

- the FPGA fabric which implements hardware blocks which communicates via the AHB bus by the firmware running on the Cortex M3 (see Fig. 3.3)

Figure 3.3: FPGA top architecture.

A Secure Digital (SDHC/SDXC) card is connected to the FPGA fabric to store the encrypted data.

## 3.2.2 Building Blocks

### Ascon

Demonstrator 2 makes use of an Authenticated Encryption cipher ASCON, a third-round candidate currently competing in the ongoing CAESAR competition. The ASCON specification describes a family of authenticated encryption designs [1]. In the framework of Work Package 4 the consortium agreed on the use of an instantiation dubbed "ASCON-128a", which is short for  $ASCON_{12,8}$ -128-128. This instantiation can process two inputs, metadata and plaintext, in 128-bit blocks, and produces a ciphertext and tag by encrypting the plaintext, and authenticating both metadata and plaintext. The plaintext can be empty to obtain a pure message authentication code ("integrity-only mode").

In demonstrator 2, ASCON is used at every step:

- in authentication mode only and in encryption mode in the two-factor authentication protocol (see below),

- in encryption and authentication mode during the data encryption process.

The algorithm used in the demonstrator is fully implemented in the FPGA. The core is a

slightly modified generic implementation from [2]. The core is wrapped in a block which adapts it to the demonstrator needs – fixed lengths of associated data, sector plaintext and ciphertext.

### TERO-PUF with Post-processing

The implemented PUF is composed of 128 TERO cells, two counters and a subtractor. The protocol to generate a 2-bits response to a challenge is the following:

- 1. Select the pair of TERO cells to be compared

- 2. Activate the TERO cells (ctrl signal = 1) for  $2\mu s$

- 3. Deactivate the TERO cells

- 4. Generate a strobe (which means subtractor output is ready to be stored)

- 5. Reset counters

This is done for all implemented TEROs and the resulting bits are concatenated to form a 128-bits response. The response is stored in a shift register.

PUF – TERO cells and counters are implemented in FPGA. The output value from the PUF hardware block is post-processed by firmware in the ARM processor. The post-processing follows all the recommendations of [8]:

- **Majority voting** the reference response is defined as the most likely response over the first 50 readouts during enrollment ;

- **Dark bit selection** the 13 least stable bits during enrollment are discarded as dark bits. We therefore end up with a 115 bit PUF response ;

- Kang's scheme to reconstruct the PUF, Kang's scheme is used as described in [5]. The helper data needed for PUF reconstruction is stored in eNVM ;

- Golay code the error correction code is Golay code (23, 12, 7) running in five loops.

### PLL-based TRNG with Embedded Tests

Demonstrator 2 uses a TRNG with online tests and cryptographic post-processing that has been provided in the framework of T2.1 as a functional block in VHDL. The demonstrator platform features a physical TRNG, which uses differential jitter between clock generated in two PLLs as a source of randomness. The TRNG implemented in Demonstrator 2 uses the Total failure test (test  $T\theta$ ) and On-line tests (tests T1 and T2) described in D4.1 [7]. Each call to this embedded TRNG produces 128 bits of random data.

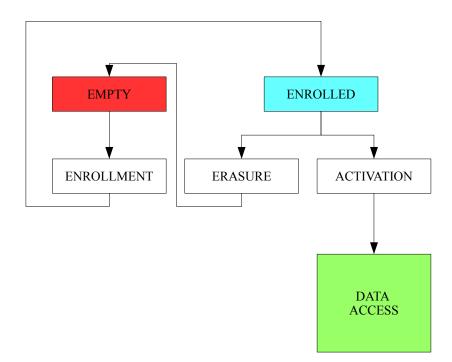

### Passphrase